Company

-

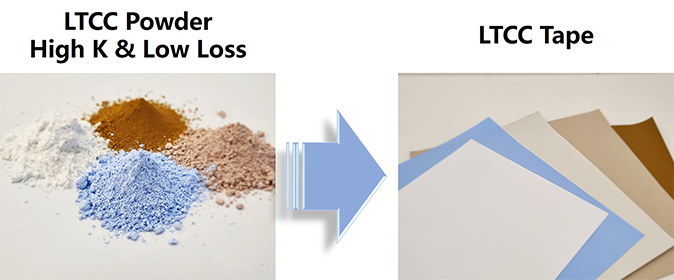

Powder(材料)

-

LTCC专用Powder(RNE-40)为Glass Free且介电损耗值低,

因此,可应用于High-Q Capacitor、Bluetooth & W-LAN Filter及Duplexer等各类部件。根据各种原材料和添加剂组合物的使用和经验,LTCC专用Tape可制成30 ~ 250 µm

的各种厚度,随时应用于各类部件。

6G通信组件

- 6G候选频段

-

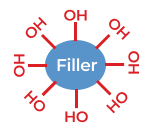

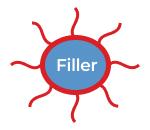

为了满足5G/6G通信材料的要求,需要确保低介电-低损耗特性。为此,我们确保拥有在高频段具有稳定特性的陶瓷材料和内化合成技术,通过表面改性工程成功开发出最佳材料。

为了提高介电性能,我们正在研制具有耐热性和耐久性的Polymer和复合材料,开发可用于各种行业的材料。此外,我们还在开发可提升高速/集成模块散热特性的材料。

- Action item

-

- mm-Wave通信频段低介电-低损耗陶瓷成分设计及合成

- 介电陶瓷纳米粒子表面活化技术

- 有机-无机杂化低介电-低损耗材料合成

1st Treatment

2nd Treatment

Ceramic-Polymer Mixture

Ceramic-Polymer

Composite Sheet

Composite Sheet

材料和工艺

- 低损耗

-

- 采用导电性优良的银电极。

- 采用自主研发的陶瓷材料,

介电损耗低。

- 机械可靠性

-

- 热膨胀系数与半导体

传感器相似。 - 机械可靠性优于传感

器封装PCB。

- 热膨胀系数与半导体

- RN2专业技术

-

- 确保原材料、设计、

加工等整个工艺拥有

自主技术。 - 可根据项目选择经过

优化的材料和工艺。

- 确保原材料、设计、

- 3D多层电路

-

- Build-up Via工艺操作简单。

- 可制作10 Layer以上

的多层电路。

Road Map

- PRESENT (5G)

- NEXT-GENERATION (5G-A)

- FUTHER EVOLUTION

Coverage Area

| 2024 | 2025 | 2026 | 2027 | 2030 | ||

|---|---|---|---|---|---|---|

| Low band | <1GHz | &Service | ||||

| Lower-Mid Band | 1~7GHz | Sample | Service | Service | ||

| Upper-Mid Band | 7~24GHz | Sample | ||||

| High Band | >24GHz | TBD | ||||

Material

| LTCC | Composite | LTCC | Composite | Composite | ||

|---|---|---|---|---|---|---|

| 介电常数 | - | 7.8 | <4 | 6.9 | <3.5 | <3 |

| 介电损耗 | - | <0.0015 | <0.005 | <0.001 | <0.003 | ≒0.001 |

| Tg | ℃ | >600 | >100 | >600 | >120 | >120 |

| Td | ℃ | - | >300 | - | >400 | >400 |

| CTE | ppm/℃ | 5.8 | 15~20 | 5.3 | 10~15 | 10~15 |

| 导热系数 | W/(m⋅K) | 3.3 | 0.5 | 4.6 | 2~3 | 2~3 |

| 吸湿率 | % | - | 0.2~0.4 | - | <0.2 | <0.2 |

| 弯曲强度 | Mpa | 320 | - | 230 | - | - |

| 剥离强度 | kgf/cm | - | >1 | - | >1 | >1 |

Circuit

| 图案 Line/space | ㎛ | 100/100 | 100/100 | 100/100 | 50/50 | 50/50 |

|---|---|---|---|---|---|---|

| 电阻率 | uΩ·㎝ | <3 | <20 | <3 | <5 | <5 |

| 附着力 | - | - | 5B | 5B | 5B | 5B |

Foundry Service

- Foundry Service

-

Foundry Service是我们根据客户提供的产品Design,采用LTCC陶瓷工艺制作和供应产品的业务。我们采用独创的LTCC陶瓷材料和材料制造技术以及20多年的LTCC工艺技术,为客户提供产品制造服务。

与塑料PCB相比,LTCC是一种强度更高、耐热性更好的PCB材料,在极端环境下有局限性的材料中具有强竞争力。

此外,基于我们多年积累的技术和全球业务经验,我们可有效缩短供货时间,确保具有价格竞争力和质量可靠性,提升客户进入市场时的竞争力。- 강점 (Strength)

-

- 建设从原材料到基板的整条生产线

- 100%全检,品质保证。

- 确保材料、电路和工艺的设计能力。

- 拥有多年积累的技术和全球业务经验。

- 快速响应(一般PO交货时间为6周)。

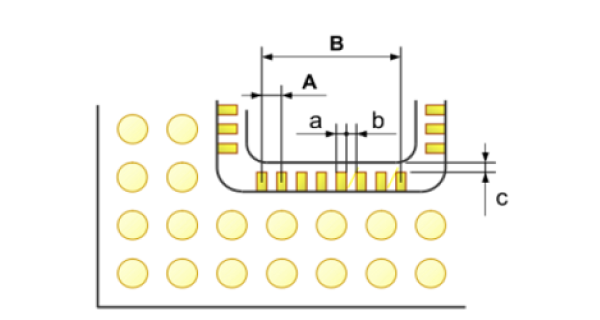

Wire Boarding Pad

| Item | Standard | |

|---|---|---|

| a | Pad width | Min 200 um |

| b | Pad space | Min 100 um |

| c | Pad to Cavity | Min 200 um |

| A | Pad Pitch accuracy | ST ± 10% |

| B | Pad Pitch accuracy (Outer to Outer) |

ST ± 10% |

ST: Size Tolerance

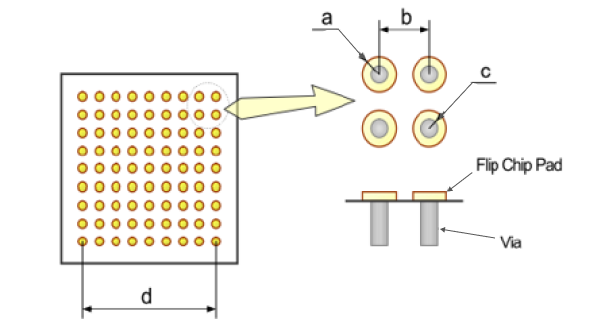

Flip Chip Pad

| Item | Standard | |

|---|---|---|

| a | Pad diameter | C + 100 um |

| b | Pad Pitch | a × 3 |

| c | Via diameter | Min 100 um |

| d | Distance between pad (Right end to Left end) |

ST ± 10% |

ST: Size Tolerance

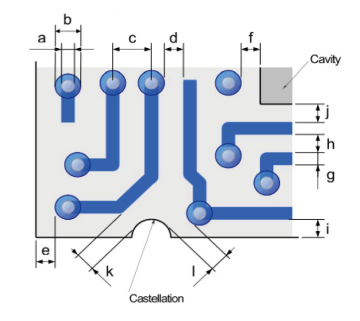

Exposed signal & Buried signal conductor

| Item | Standard | |

|---|---|---|

| a | Via diameter | Min 100 um |

| b | Via hole cover diameter | Via dia + 100 um |

| c | Via hole pitch | a × 4 |

| d | Via cover to line | Min 125 um |

| e | Via cover to substrate edge | Min 150 um |

| f | Via cover to cavity edge | Min 150 um |

| Item | Standard | |

|---|---|---|

| g | Line width | Min 100 um |

| h | Line spacing | Min 100 um |

| i | Line to substrate edge | Min 150 um |

| j | Line to cavity edge | Min 200 um |

| k | Castellation to line | Min 300 um |

| l | Castellation to line | Min 300 um |

ST: Size Tolerance

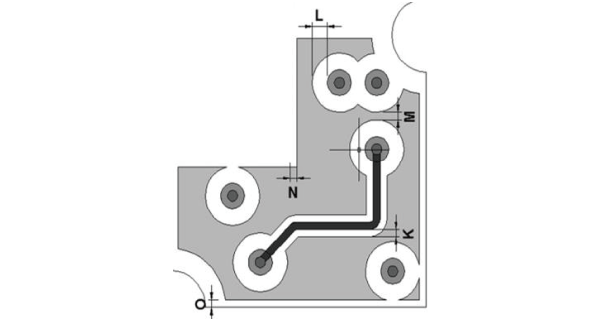

Ground Plane

| Item | Standard | |

|---|---|---|

| K | Line to GND | Min 150 um |

| L | Isolation gap | Min 200 um |

| M | Solid plane | Min 200 um |

| N | Cavity edge to GND | Min 300 um |

| O | Substrate edge to GND | Min 300 um |

ST: Size Tolerance

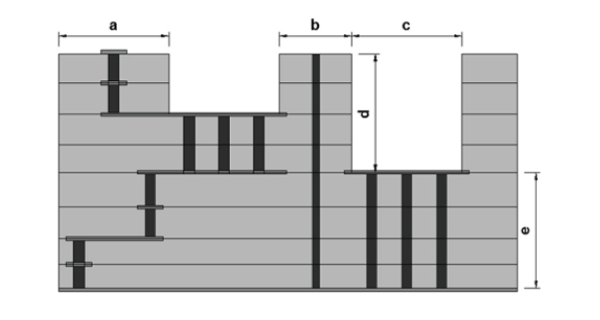

Cavity Design

| Item | Standard | |

|---|---|---|

| a | Substrate edge to cavity edge | Min 2.0 mm |

| b | Cavity to cavity gap | Min 2.0 mm |

| c | Cavity width | Min 2.5 mm |

| d | Cavity height | Min 0.5 mm |

| e | Thickness under the cavity | Min 1.0 mm |

ST: Size Tolerance